**Handels GmbH**

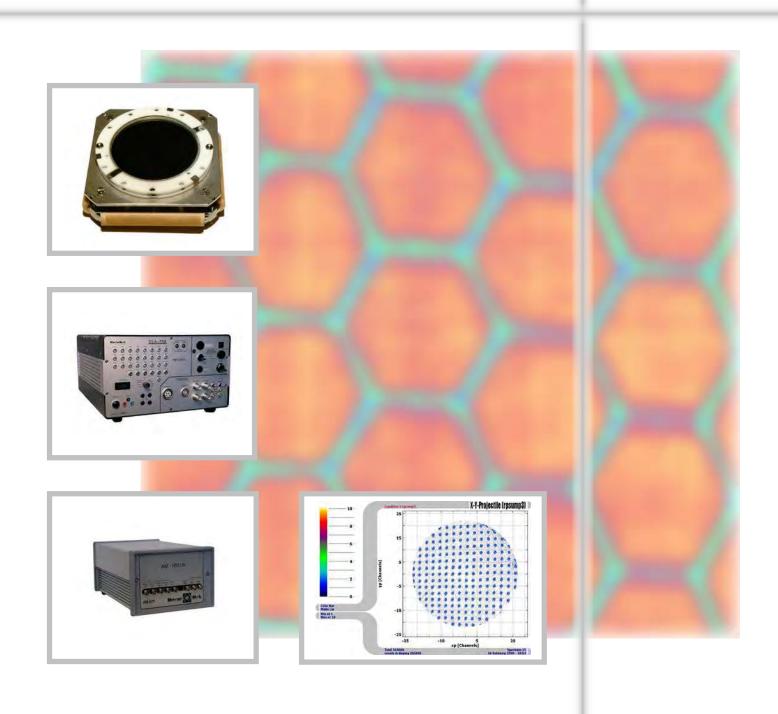

Supersonic Gas Jets

Detection Techniques

Data Acquisition Systems

Multifragment Imaging Systems

# MCP Delay Line Detector Manual

(Version 11.0.1304.1)

#### Mail Addresses:

#### **Headquarter**

**RoentDek** Handels GmbH Im Vogelshaag 8 D-65779 Kelkheim-Ruppertshain Germany

### Frankfurt branch

RoentDek Handels GmbH c/o Institut für Kernphysik Max-von-Laue-Str. 1 D-60438 Frankfurt am Main Germany

Web-Site:

www.roentdek.com

WEEE:

DE48573152

Product names used in this publication are for identification purposes only and may be trademarks of their respective companies.

All rights reserved. Technical changes may be made without prior notice. The figures are not binding.

We make no representations or warranties with respect to the accuracy or completeness of the contents of this publication.

# Table of Contents

| DETEC        | TOR SYSTEM - COMPONENTS                                              | 5  |

|--------------|----------------------------------------------------------------------|----|

| 1 TH         | E MICROCHANNEL PLATE DETECTOR WITH DELAY-LINE ANODE                  | 7  |

| 1.1          | GENERAL DESCRIPTION                                                  | 8  |

| 1.1.         |                                                                      |    |

| 1.1.         |                                                                      |    |

| 1.2          | ASSEMBLY OF THE MCP-DETECTOR                                         | 11 |

| 1.2.         | .1 List of Detector Assembly Parts                                   | 11 |

| 1.2.         |                                                                      |    |

| 1.2.         | o v                                                                  |    |

| 1.2.         |                                                                      |    |

|              | .2.4.1 Assembly of the MCP-stack for the DLD40, DLD80 and HEX80      | 14 |

|              |                                                                      |    |

| 2 M(         | DUNTING OF THE DETECTOR AND CABLE CONNECTIONS VIA VACUUM FEEDTHROUGH |    |

| 2.1          | MOUNTING OF THE DETECTOR ON A VACUUM-FLANGE                          |    |

| 2.2          | CONNECTING THE SIGNAL CABLES TO A FEEDTROUGH FLANGE                  |    |

| 2.3          | THE FT12TP (HEX) – FEEDTHROUGH FLANGE WITH SIGNAL DECOUPLER          |    |

| 2.4          | THE FT4(TP) FOR FT16(TP) AND DET40/75                                |    |

| 2.5          | OPERATION OF THE MCP DETECTOR WITH DELAY-LINE (OR TIMING) ANODE      |    |

| 2.5.         |                                                                      |    |

| 2.5.         | r                                                                    |    |

| 3 TH         | E FRONT-END TIMING ELECTRONICS MODULES: AMPLIFIER & CFD MODULE       | 35 |

| 3.1          | SIGNAL INPUTS AND AMPLIFICATION                                      | 36 |

| 3.2          | THE DLATR BOARD                                                      | 38 |

| 3.3          | CFD CONTROLS AND OUTPUTS                                             |    |

| 3.4          | CONNECTING AND OPERATING THE ATR19                                   |    |

| 3.5          | OPENING THE ATR19 MODULE                                             |    |

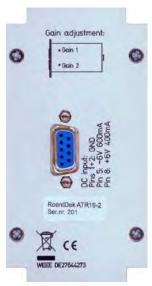

| 3.6          | THE ATR19-2(B) MODULE                                                |    |

| 3.7          | FINAL ADJUSTMENT FOR DETECTOR OPERATION                              |    |

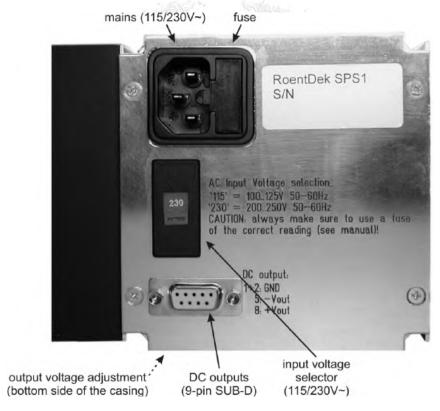

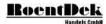

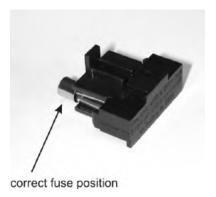

| 3.8          | THE SPS1(B) MAINS ADAPTER                                            |    |

| 3.8.         |                                                                      | 46 |

| 3.8.         | 11.5                                                                 |    |

| 3.8.         | 1 (1/2000)(0.57)                                                     |    |

| 3.8.         | C C C C C C C C C C C C C C C C C C C                                |    |

| 3.8.         |                                                                      |    |

| 3.9          | TROUBLESHOOTING THE ATR19'S INTERNAL MAINS POWER SUPPLY              |    |

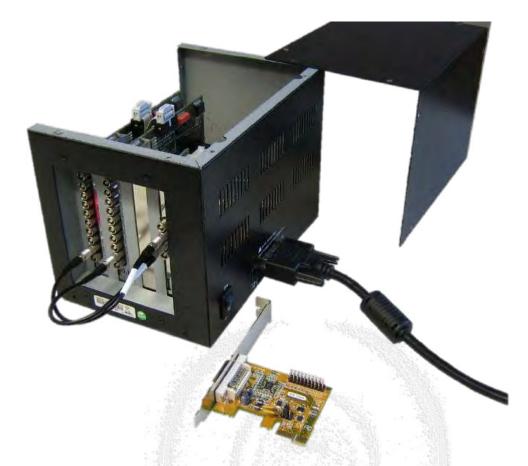

| 4 DA         | TA ACQUISITION HARD- AND SOFTWARE                                    |    |

| 4.1          | THE TIME-TO-DIGITAL-CONVERTERS (TDC) FOR PC                          |    |

| 4.1.         |                                                                      |    |

| 4.1.         |                                                                      |    |

| 4.1.         |                                                                      |    |

| 4.2          | HARD- AND SOFTWARE INSTALLATION                                      |    |

| 4.2.         |                                                                      |    |

| 4.2.<br>4.2. |                                                                      |    |

|              | CONNECTING THE ATR19 OR CFD WITH THE TDC                             |    |

| 4.3<br>4.3   |                                                                      |    |

| 4.3.<br>4.3. |                                                                      |    |

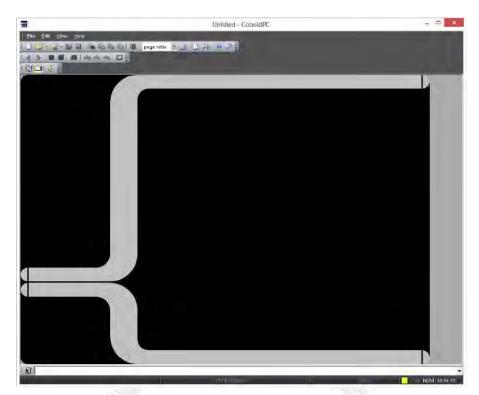

| 4.3          | STARTING THE COBOLDPC 2011 R3 SOFTWARE:                              |    |

| 4.4<br>4.4   |                                                                      |    |

| 4.4.<br>4.4. |                                                                      |    |

| 4.4.         |                                                                      |    |

|              | GH VOLTAGE SUPPLIES                                                  |    |

| э піч        | OH VOLIAGE SULLLES                                                   | US |

# Roent Dek

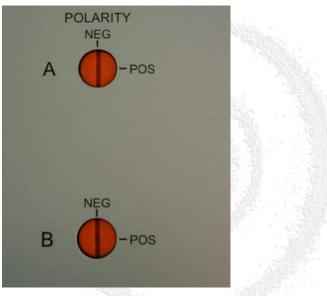

| 5.1    | THE HV 2/4 DUAL HIGH VOLTAGE SUPPLY MODULE | 69 |

|--------|--------------------------------------------|----|

| 5.2    | THE BIASET3 WITH SPS2(MINI)                | 71 |

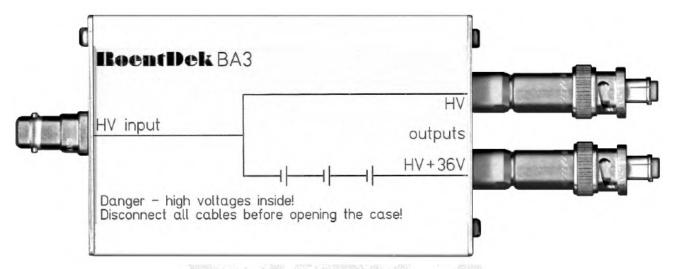

| 5.3    | BA3 BATTERY UNIT                           |    |

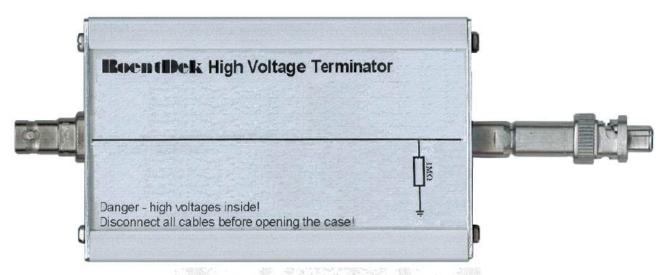

| 5.4    | HVT AND HVT4 HIGH VOLTAGE TERMINATORS      | 74 |

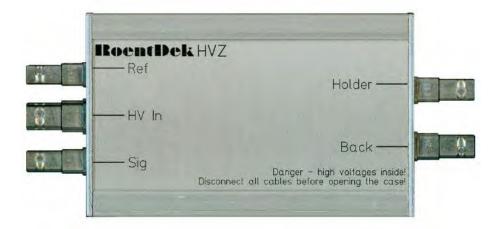

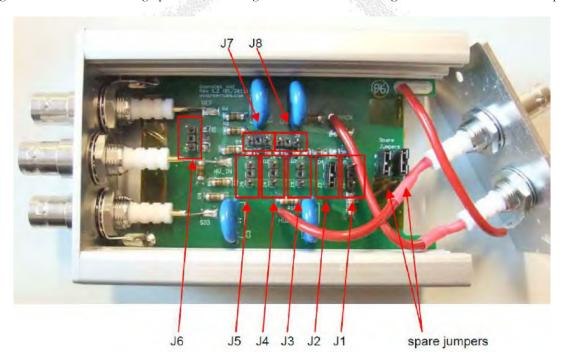

| 5.5    | HVZ VOLTAGE DIVIDER UNIT                   | 75 |

| APPE   | NDIX: (MCP'S):                             | 79 |

| LIST ( | OF FIGURES                                 | 81 |

| LIST ( | OF TABLES                                  | 83 |

|        |                                            |    |

# Detector System - Components

This manual describes all major components of the **ExcentDek** delay-line detector system as it can be delivered for the **DLD40(EP)**, **DLD80(75eT)**, **HEX80/HEX75** and **DLD120** and **HEX120(100)** detector. Even if you have not purchased the complete system you will find valuable information in the chapters describing the different components about the link between the components and the operation. However, you might have received only the relevant parts of this manual.

- 1. DLD or HEX microchannel plate detector with delay-line anode

- **0. FT12(16)TP** 12-pin CF35 (and fourfold MHV) UHV-feedthrough flange(s) with signal decouplers and (optional) flange mounting gear on DNxxxCF flange with CF35 ports (xxx = 100 300)

- **0. ATR19** fast (differential) amplifier unit with integrated constant-fraction-discriminator (default) or **FAMP8** (or similar) amplifier unit, **CFD8c/**7x: (or similar) constant-fraction-discriminator modules (for download)

- TDC8HP or HM1 time to digital converter and CoboldPC read-out software (default) or fADC4/8 fast ADC units (for download)

Error! Reference source not found.. HV2/4, BIASET3 or similar high voltage supply assembly and BA3/HVT/HVZ auxiliary bias units.

Please follow the link <a href="http://www.roentdek.com/manuals">http://www.roentdek.com/manuals</a> for device specific manuals.

If you have received special detector components, i.e. a detector of different size or type, or other electronic modules you will find a separate manual commenting on peculiarities of your special system. In this case the information given here is mostly relevant for your system but you might need extra information. Please also refer to the FAQ document on the web page.

Please always check our web site for updates after you have received our products or contact **RoentDek**.

# 1 The Microchannel Plate Detector with delay-line anode

The Micro-Channel Plate detector with delay-line anode is a device for single particle/photon counting, giving information on the position of each particle/photon and its impact time with high precision. It uses an electronic read-out scheme employing fast timing amplifiers, timing discriminators and digitizers. It operates under ultra-high vacuum and requires high voltage supplies.

This detector system is modular and com in different sizes and versions.

#### Typical performance:

position resolution < 0.1mm overall linearity 0.3mm rate capability 1MHz multi-hit dead time 10-20ns

#### Typical characteristics of MCPs (for DLD40EP, DLD75eT and HEX75 see below)

# of MCPs in stack

Outer Diameter: 50/86.6/127mm Active Diameter: 45/80/120mm

Aspect Ratio L/D 60:1

Thickness 1.5mm

Pore size 25 $\mu$ m

Center-to-center spacing: 32 $\mu$ m

Bias Angle: 8° ± 1°

Open Area Ratio: >50%

for **DLD40EP** MCP: 40mm OD (>40mm active), L/D 80:1, 1mm thickness, 13 $\mu$ m pore size, bias angle: 20°, OAR > 70% for **DLD75eT** MCP: 86.7mm OD (75mm active), L/D 80:1; 1mm thickness, 13 $\mu$ m pore size, bias angle: 19°, OAR 64% for **HEX75** MCP: 86.7mm OD (75mm active),L/D 40:1; 1mm thickness, 26 $\mu$ m pore size, bias angle: 20°, OAR 70% The **HEX75** uses triple MCP stacks (Z-stacks). Other detectors can also be delivered with triple MCP stacks (option .../Z) The **HEX120** can also be delivered as **HEX100** with 114mm OD MCP (105mm active), 26 $\mu$ m pore size, bias angle: 20°, OAR 70%

## Typical characteristics of the detector assembly

Height above a mounting Flange: about 100mm (adjustable)

Mounting Diameter: 94/144/196/246mm

Operating Temperature Range: -50 to 70°C

Operating Pressure: < 2 x 10-6mbar

Baking Temperature: 150°C Maximum

Electron Gain @ 2400Volts\*: 10<sup>7</sup> Minimum

If you have chosen a detector set with central hole, its size in the MCP is usually 6.4mm and the minimum active diameter 9mm.

If you have chosen a different custom detector type, e.g. DLD25, DLD80x100, DLD100, DLD150, or HEX40 please refer to the separate instructions.

<sup>\*</sup> For **DLD40EP**, **DLD75eT** or **/Z** options: about 300V higher voltages may be applied.

## 1.1 General Description

The **RoentDek** MCP detector with delay-line anode is a high resolution 2D-imaging and timing device for charged particle or photon detection at high rates with limited multi-hit capability. The linear active diameter is at least 40mm for the detectors with the **DL40** anode (e.g. **DLD40** and **DLD40EP**), 75mm for the **DL80** anode (e.g. **DLD80** and **DLD75eT**), and about 120mm for the **DLD120**. The **RoentDek Hexanode** has a third delay-line layer that gives redundant detection opportunities either to improve the multi-hit performance, linearity or to allow the use of a MCP setup with central hole and minimized blind detection area. In its usual version (**HEX80**) it has about 75mm redundant detection area (**HEX120**: 100mm redundant, up to 115mm linear with at least two layers, total up to 120mm, **HEX100**: 100mm redundant detection area, **HEX40**about 40mm redundant detection area)\*. For detectors with central hole (e.g. **HEX40/o** and **HEX80/o**) the descriptions in this manual are also relevant unless otherwise stated. A **DLD150** version is available on demand with 150mm active detection diameter.

The detector consists of a pair of selected MCPs in chevron configuration or of a triple stack (Z-stack) and a helical wire delay-line anode for two-dimensional position readout. The MCPs are either supported by a pair of partially metalized ceramic rings (1.5/2mm thick, 65/105mm outer diameter for **DLD40/DLD80** and **HEX80** with metal contacts on the ceramic rings are suitable for soldering, clamping or spot welding) or the MCP stack is mounted between a metal front ring and a (usually square-shaped) rear side holder plate, e.g. for the **DLD120** and **HEX120(100)** or custom MCP stack designs.

Operation requires two DC voltages for a (resistance matched) MCP stack on front and back contacts and three voltages for the anode's support plate ("holder") and the anode wire array. All voltages can be supplied by separate HV-supplies or voltage dividers. The baking limit is specified as 150°C for the detectors and for optionally provided in-vacuum cables and feedthroughs.

The wire array consists of two or three helical wire propagation double (delay) lines. For each dimension a differential wire pair is formed by a collection (signal) wire and a reference wire. A potential difference of 20V to 50V between signal and reference wire ensures that the electron cloud emerging from the MCP is mainly collected on the signal wires, shared between the wire layers for different position encoding directions. The anode holder has to be biased with an intermediate potential with respect to the anode wires and the MCP back potential to ensure proper charge cloud propagation and spatial broadening in the drift zone between MCP and anode wires. The optimal voltage depends on the distance between the MCP holder plate and the anode wires.

Typically the wires should have about 300V more positive potential than MCP back side and the holder about +100V with respect to the MCP back potential.

Avoid penetration of strong external electrical and magnetic fields into the electron cloud drift region (between MCP and wire anode). Electrical fringing fields can produce image distortions, magnetic fields (> 50Gauss) disturb the proper charge cloud broadening and will lead to malfunction of the anode.

#### 1.1.1 Position Encoding

The position of the detected particle/photon is encoded by the signal arrival time difference at both ends of each parallel-pair delay-line, for each layer independently. While the signal speed along the delay line is close to speed of light, one can define a perpendicular signal speed  $v_{\perp}$  given by the pitch of one wire loop (typically 1mm) and the time, which a signal needs to propagate though this loop. This defines the single pitch propagation time per 1mm which is equal to  $1/v_{\perp}$  (in units mm/ns).

The corresponding ends of the delay-lines for each dimension are located on the opposite corners of the wire array terminals on the rear side. The electrical resistance of each wire is between 5 and  $100\Omega$  end-to-end, depending on the size of the delay-line and the wire type used. Corresponding ends of wires can such be identified. The four (or six) terminal pairs have to be connected to vacuum feedthroughs by a twisted-pair cable configuration (both cables of a pair must have equal lengths, within 5mm). From the feedthroughs the signals must be transmitted (after DC-decoupling) to a differential amplifier or signal transformer with equally adequate transmission cables.

The difference between the signal arrival times at the adjacent ends of each delay-line is proportional to the position on the MCP in the respective dimension. The sum of these arrival times is fairly constant with few ns for each event (see below). The time sequence of the signals can be measured by time-to-amplitude converters (TAC) or an n-fold time-to-digital converter (TDC), n is at least 4 or up to 7 (**Hexanode** with separate timing channel). As time reference the signal on the MCP back or front side can be used for correlating each particle to others or to an external trigger (TOF-measurement).

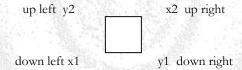

For the **DLD** detectors, the digital encoding for obtaining a 2d digital image (X/Y) is

<sup>\*</sup> In the following we will refer to those detectors using the same anode only by nominating one detector version, e.g. for **DLD40** and **DLS40eT** as **DLD40** unless otherwise noted. Additional remarks, if any, will refer to the different MCP types.

$$X = x1 - x2 + O_x$$

and  $Y = y1 - y2 + O_y$

Equation 1.1

with x1, x2, y1 and y2 denominating the time for each signal, O<sub>x</sub> and O<sub>y</sub> are arbitrary offsets.

The fast timing signal picked up from an MCP contact or, in the case of a pulsed particle/photon source, a "machine trigger" signal can serve as time reference. The single pitch propagation time (for 1mm) on the delay line is about 0.75ns for **DLD40**, 1ns for **DLD80** and 1.24ns for **DLD120**. Thus the correspondence between 1mm position distance and relative time delay in the 2d image is twice this value: about 1.5ns, 2ns or 2.5ns, respectively. Note that these numbers are only accurate within 5% and are slightly different for each dimension. In order to calculate the position in mm from the digital X and Y values you have to take into account the bin width of your TDC and the single pitch propagation time for the respective layer.

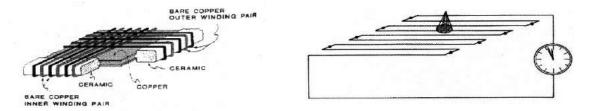

Figure 1.1: Operation principle of the delay-line-anode, left picture from: Sobottka and Williams IEEE TS-35 (1988) 348

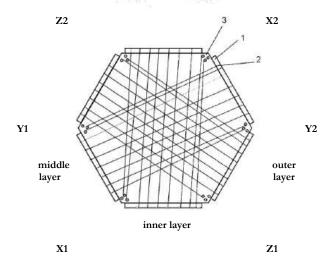

The **Hexanode** has an additional layer and gives over-determined (redundant) position information: It is possible calculating the two-dimensional particle position of signals from of any two of the tree layers. The signals from the third layer serve as a redundant source of information for cases when signals are "lost" due to electronic dead-time (multiple hit events), non-continuous winding schemes (anode with central holes) or non-perfect electronic threshold conditions/damping on special very large delay-line anodes. With the **Hexanode** it is also possible to control their delay-lines' intrinsic resolution and linearity, improving the overall imaging performance. The **Hexanode**'s coordinate frame u, v, w can be transformed into a Cartesian coordinate system by the following equations using only two of the hexagonal coordinates respectively, if the connection scheme in the next section is chosen:

$$X_{uv} = u + Ox$$

$$Y_{uv} = \frac{1}{\sqrt{3}}(u - 2v) + Oy$$

$$X_{uw} = X_{uv}$$

$$Y_{uw} = \frac{1}{\sqrt{3}}(2w - u) + Oy$$

$$X_{vw} = (v + w) + Ox$$

$$Y_{vw} = \frac{1}{\sqrt{3}}(w - v) + Oy$$

Equation 1.2

$O_x$  and  $O_y$  are arbitrary offsets. The position in a hexagonal coordinate frame is coded by the arriving time differences from signals in opposite corners of the anode as in case of the **DLD**.

$$\begin{array}{rcl} u & = & (x1-x2)*d1 \\ v & = & (y1-y2)*d2 \\ w & = & (z1-z2)*d3+o \end{array}$$

Equation 1.3

If  $1/v_i$  is the single pitch propagation time for a delay line layer i ( $v_i$  is slightly different for each layer) then  $d_i$  is given by

$$d_i = \frac{1}{2} v_i * \Delta t$$

Equation 1.4

d<sub>i</sub> must be precisely known to make the images obtained via different layer combination coherent. o is an offset value that shall unify the "time difference zero" of all three layers, i.e. it must be chosen so that geometrically the position lines for calculated u, v, w have a common crossing point, e.g. w must be zero when u and v are zero.

For the **HEX80** the single pitch delay is about 1.4ns. The exact values u, v, w, o differs from anode to anode. There relative values must be precisely determined which can be done by a self-calibration routine (for details please contact **RoentDek**). o is also a function of connection cable lengths and cable lengths all the way to the TDC/TAC inputs (and internal offsets therein) and must therefore be recalibrated whenever these parameters have changed. The single pitch delay for the **HEX120** is about 1.75ns which corresponds to a pitch of 1mm or 1.5mm, depending on the anode version which you have received (default: 1.5mm).

For detectors with central hole, the gaps in the wiring have to be taken into account. Please contact **RoentDek** for the program codes appropriate for your detector.

The linearity deviations in each delay-line layer should be calibrated to achieve optimal results. Please contact RoentDek for an auto-linearization routine and advanced position codes.

The X and Y positions can be calculated from any combination of the Equation 1.2. If for a given event more signals than from the minimum of two layers are available, it is recommended to choose signals from those two layers where the positions are most distant from the respective delay line ends (or gaps).

### 1.1.2 Timing information:

In order to determine the time difference between an outer time marker and the particle impact, the signal at the MCP contact can be used. But it is also possible to deduce the particle impact time from the delay-line signals:

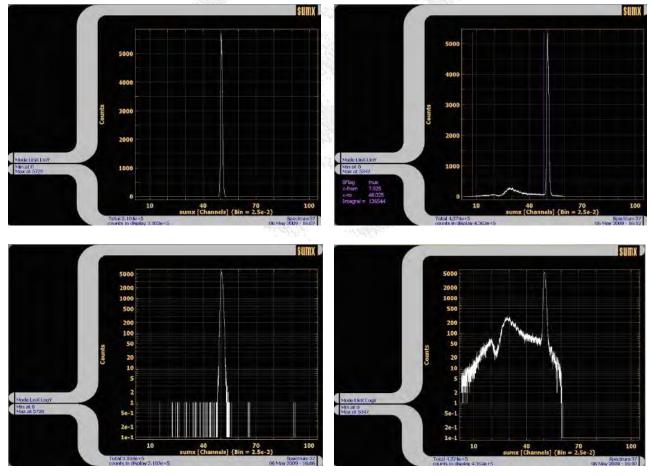

If the MCP signal is used as the time-zero, the "time sum" values

```

sumx = x1 + x2

sumy = y1 + y2

sumz = z1 + z2 (only available for Hexanodes)

```

#### Equation 1.5

are constant within the time resolution (less than one ns) but have a slight "position walk" which can be determined by plotting sum vs. difference (i.e. position). Thus it is also possible to deduce the particle impact time from these time sum values alone. Even if the particle timing is not of interest, the time sum measurement can be used to verify a proper detector function.

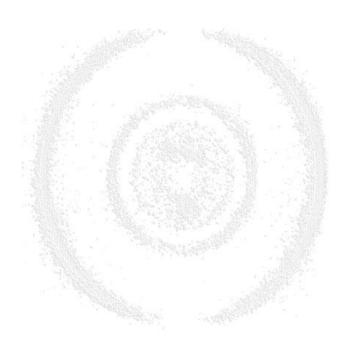

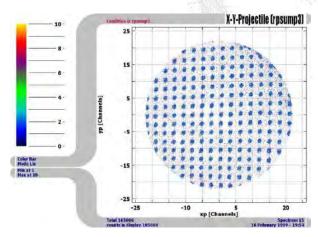

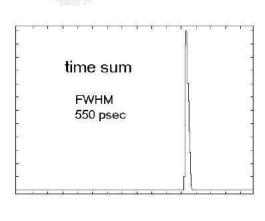

Figure 1.2: Typical imaging/timing performance of a DLD40 detector. The detector (shaded by a mask) was irradiated with  $\alpha$ -particles. Similar or better results can be achieved with adequate read-out electronics. Temporal resolution is significantly better than the local time sum width (see right picture) which indicates an upper limit.

## 1.2 Assembly of the MCP-Detector

The assembly should take place under clean and dry conditions.

#### 1.2.1 List of Detector Assembly Parts

- ceramic rings, partially metal coated (for DLD40, DLD80 and HEX80/HEX75) or metal rings/plates

- two multi-channel plates, selected for chevron configuration, matched in resistance

- metal spring clamps (for DLD40, DLD80 and HEX80/HEX75)

- plastic M3 screws with nuts (for DLD40, DLD80 and HEX80/HEX75 only during assembly of the MCP holder)\*

- 1 delay-line anode

- Assorted small parts for cable connections (optional)

If you have purchased the detector with the "readily mounted" option (only available with FT12(16)TP/xxx flange mounting) you need to remove the detector case (and ma return it to **BoentDek** for receiving a refund). All connections to the anode should already be in place but the MCP must be mounted according to the directions below. You will also have to verify all anode connections and check for absence of shorts which may have occurred during transports. Therefore, please review the following instructions even if you have received a "readily mounted" anode.

For **DLD40**, **DLD80** and **HEX80** the MCP holder with rear ceramic ring may already be placed on the delay-line anode, it is fixed by the retractable "shields" in a position that should be resumed after assembly of the MCP stack. If the rear ceramic ring is not pre-mounted (i.e. for transport safety reasons) please test-mount it now and observe the relative angle of the metallization structure. You will in any case have to remove it for assembling the MCP stack (see below). After this assembly, the rear ceramic ring has to be in about the same orientation as shown in Figure 1.3.

All parts, especially the MCP and the wire anode structure should be handled with great care. The wire array is very delicate. The ceramic rings should not be exposed to exceeding mechanical or thermal stresses. The MCP surfaces are very sensitive and should never be touched or scratched. Some "optical defects" may be seen on the MCP surfaces after removing them from the transport packing. Unless the MCP are broken (transport damage) this will not affect performance within specifications. Please read the whole assembly section before starting the mounting, see also Appendix for MCP handling.

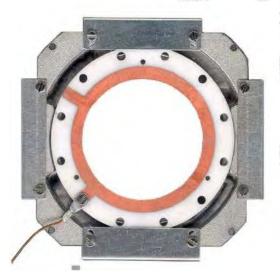

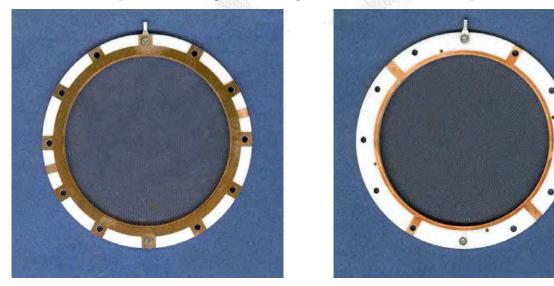

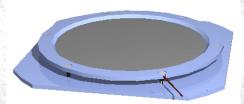

Figure 1.3: Orientation of the rear ceramic ring on the Delay-line assembly (DLD40, DLD80). For HEX80/HEX75 the orientation is similar, but there is only one pair of flat "shields".

#### 1.2.2 Preparation

1. Verify with an Ohm meter that no dust particles have electrically shortened the anode wires. The anode contains one pair of wires for each special direction. Neither the two wires of one pair nor the wires of the different layers should be in contact (>10M $\Omega$ ). Also verify that there is no electrical connection between the wires and the holder plate. Dust particles can be removed by gentle blow with dry air or a soft brush. Check the resistance of each of the 4 wires. From one end to the other it should be around 5 $\Omega$  for the **DLD40**, 12 $\Omega$  for the **DLD80**, 17 $\Omega$  for the **HEX80/HEX75**,

<sup>\*</sup> For **DLD120** and **HEX120**: 6 PEEK M3 screws and 3 plastic M3 rods (the latter only during assembly of the MCP holder)

$25\Omega$  for **DLD120** and about  $40\Omega$  for the **HEX120**. These are the values for the standard **RoentDek** anodes. If you have ordered and received a special type, the resistance might be different. Note, that even after testing for the absence of a short between wires, at any time, after assembly, installation, baking or after biasing the detector, a metallic dust particle from the environment can short signal and reference wires. If such a problem persists contact **RoentDek** for advice.

For **DLD120** or **HEX120** please continue with (4).

- 2. Remove the ceramic ring from the assembly (if pre-mounted). Two of the shields can be retracted to liberate the stack after the M2 screws are loosened. Note, that the shields must not touch any contacts on the ceramic rings and that the spring clamps that hold the stack together are mounted with about 45° angle with respect to the delay line so that they are not touching any metal part. This orientation has to be resumed when re-assembling the detector.

- 3. Optionally: a mesh can be glued, soldered or spot-welded directly onto the front side of the *front* ceramic ring, such being at a position of 1.5/2mm in front of the MCP surface. However, we recommend using one of the **RoentDek** detector meshes of type (w)Mesh 40/80/120 which can be mounted to the front ring.

- 4. Prepare the connection cables for the MCP detector and the delay-line anode. If you have ordered a **FT12(16)TP** you should have received these connection cables. For the MCP and holder connection 3 (single) cables are used. For the anode 4 or 6 (Hex) cable pairs with proper impedance (ideally 100-150Ω) are needed. Unless you have received special cable pairs or twisted pairs with adequate lengths you must form twisted cable pairs: The two cables of a pair must have equal lengths within a few mm. The pair must be twisted at least 3 turns per 10cm to form a well-transmitting twisted pair cable line. For connecting these cables to the delay-line terminals special 2mm connector pins are provided. The three other single cables are needed for "MCP front", "MCP back" and "Holder" which is the metal anode body (see also next section). A fourth single cable can be used for connecting a mesh.

- 5. For **DLD40**, **DLD80** and **HEX80**: The cables for the MCP connections can be soldered or spot-welded directly onto the metallization of the ceramic rings or clamped to the ring with special recessed M2 nuts and screws (obtainable form **BoentDek**). Also special 3mm and/or 2mm lugs for crimping a cable can be supplied. If soldering preferred use the metallization strips which are *not* located at a hole of the ceramics. Do that *before* mounting the MCP. Alternatively a set of special M2 nuts with short M2 screws can be provided for clamping, or special spring clamps that can be placed between the rings at the position of a metallization located on a hole. Contact one side of each ring with a cable to bias "MCP back" and "MCP front" respectively.

For **DLD120** and **HEX120** or **100**: The cable for the "MCP back" connection can be fixed by a M2 screw to the rear MCP plate. The cable for the "MCP front" connection is either clamped to the front ring with one of the M3 polyimide screws or for newer systems alternatively via an M2 screw that can be fixed to the front ring (see also Chapter 1.2.4.2).

A cable for the anode "holder" can be connected anywhere on one of the metal M2 rods in the anode, or any part electrically connected to that, see **Error! Reference source not found.**.

You may clean all parts *except the MCPs* in an ultrasonic bath for a few minutes with a mild alcoholic solvent like isopropanol. MCP should only be exposed to a cleaning procedure if they have some surface contamination that cannot be removed by spraying with dry air. Please contact **EcentDek** for further advice. For MCP general handling see also instructions on the manufacturer's web sites or in the Appendix of this manual. Touch MCPs only with care along the rim, preferably with gloves. If the MCPs need replacement mount a set with matching electrical resistance only.

Alternatively **RoentDek** can supply an intermediate shim ring with bias contact lug on demand.

Now the detector can be finally assembled, preferably under clean room conditions

### 1.2.3 Connecting the Wires to the Delay-line Anode

A proper design and use of connection cables is essential for a decent detector performance. Therefore we strongly recommend using the feedthroughs of type **FT12** for the delay-line connections (**DLD** and **HEX**). For the **DLD** the **FT12** can also accommodate the bias for the other detector parts, while for the **HEX** an additional feedthrough set is required to connect Holder, MCP front and MCP back (and an optional mesh), for example the **FT4\***. Please refer to Chapter 0 of the manual

<sup>\*</sup> The FT4 and FT12 are combined to the FT16 feedthrough set for HEX detectors

even if you have not purchased this option because important features for proper cabling and signal decoupling circuits are described there.

You need a set of 4 (Hexanode: 6) twisted pair cables to connect the anode wires. In the four (six) corners of the anode's rear side each pair must be connected to the wire terminals formed as M2 stubs, preferably with the connector pins provided. Mounting the cable in a different way (i.e. by M2 nuts) is possible but not recommended, see also Chapter 0. Note that the M2 stubs are not secured against torque. If you have purchased the **FT12(16)** feedthroughs adequate cables with adequate connector pins/lugs for both ends are provided with it. Use only so much force that the cables are safely connected and are not moving when gently wiggling on them. Also connect the anode holder with a cable, wherever suitable (see also below). This cable has to supply the anode holder potential.

Figure 1.4: Cables for holder and wires on DLD40, DLD80 and HEX80. The four M2 rods and the MCP holder plate are on the same "Holder" potential as the delay-line anode body. The cable can be connected anywhere on these parts.

Please note that this is NOT the case for the DLD120 and Hex120(100) assemblies where the MCP back plate is insulated from the Holder and carries the MCP back potential.

Before connecting the cables to a feedthrough it is important to distinguish the cables that lead to ends of the same single delay line wire. Both ends must receive the same voltage ( $U_{ref}$  or  $U_{signal}$ , see Chapter 2.2).

In order to later obtain an image on the PC monitor according to a phosphor screen (rear) view, the following connection scheme in the corners is recommended for the **DLD** detectors.

Figure 1.5: Orientation of x and y position terminals on anode viewed from the rear side, the outer delay line wires In this position the sliding shields are recommended to be placed left and right on the (inner) Y-layer side.

For the **Hexanode**, the following wiring scheme is mandatory to comply with the position computations in Equation 1.2:

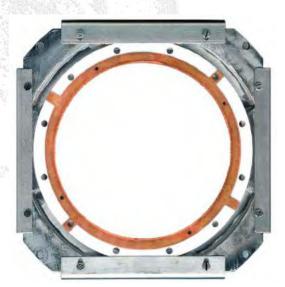

Figure 1.6: Rear view of a Hexanode with suggested cable connection

### 1.2.4 Assembly of the MCP-stack

If you have received a DLD120 or HEX120(100) please refer to Chapter 1.2.4.2

#### 1.2.4.1 Assembly of the MCP-stack for the DLD40, DLD80 and HEX80

A cartoon about the assembly of the MCP stack for the **DLD40**, **DLD80** and **HEX80** can be found on our web-site in the *MOVIES* section. There you can also find cartoons showing the mounting of the MCP stack to the anode.

By now you have to decide if you prefer to solder the cables for the MCP contacts directly to the contact pads on the ceramic ring, as recommended. Note, that even for UHV environment small amounts of lead-free solder/flux are usually tolerable. All parts should be cleaned after the soldering.

If you prefer not to solder the cables to the ring, fix a cable with the provided M2 screw with the special nut on the front ceramic ring now. The cable can either be crimped to a contact lug and fixed with a M2 screw or wound around this screw without using the lug.

If you prefer not to solder the cables directly onto the rings and have received (or prepared your own) connecting lugs and a screw set fix a cable to the front ceramic ring now. The cable to the feedthrough must first be crimped (or soldered) to the contact lug with 3mm eye-let and fixed with a special recessed M2 nut and a countersunk M2 screw (4mm long for **DLD80/HEX80** or 3mm long for DLD40), see Figure 1.7.

If you have purchased a mesh from **RoentDek** you may mount it now to the front side of the front ceramic ring with the same (or other) recessed M2 screws/nuts at a desired distance from the front ring. It should be fixed on at least two (for zero distance) or more positions and must be connected with a bias cable to a feedthrough. If you have purchased any of the **FT12(16)TP** products you may connect this bias cable to the "X" line on pin1 of the **FT12TP** or in case of **HEX**, to the vacant MHV/SHV feedthrough on the **FT16TP** feedthrough assembly (it is then recommended also using a **HFST** for biasing the mesh, see Chapter 0

Figure 1.7: Connections to a ceramic ring. Left: cable clamped to a "front" ring (MCP side visible). Middle/right: cable clamped to a back ring with 3mm lug, countersunk M2 screw and special M2 nut.

Figure 1.8: Free-standing mesh mounted to the MCP front ring (left: front side, right rear side of the front ring).

Depending on the connecting scheme of the MCP contact there may be mechanical conflicts for the mesh mounting and/or potential electrical hazards for the detector operation at certain mesh voltages. We recommend contacting **RoentDek** for further advise when using a mesh close (i.e. < 3mm distance) to the MCP front ring.

The MCP back contact on the rear ceramic ring can be made in the same way as on the front ring. For most standard **RoentDek** detector stacks with a total MCP stack thickness of 3mm (not for **DLD40EP** and **DLD80eT/Hex75eT**) the cable for biasing the MCP stack's back side can alternatively be connected via a contact spring clip (see Figure 1.17).

#### It is very important

- that no part of the screw/nut protrudes more than 0.8mm towards the holder plate (a screw tip must end in a recessed nut or just on the nut edge). Use only countersunk M2 screws for fixing things on the ceramic rings.

- to rotate the ring on the holder plate such that the screw is located at or near the holes along the diagonal (see Figure 1.8). Any other contact or mounting screw (i.e. for a mesh) cannot be on the same azimuthal position later.

Figure 1.9: Recommended ring orientations on a DLD40 assembly (DLD80 & HEX80 similar). Left picture: cable connection of this type without lug. Cable connection pads must rest in the recessed parts of the holder plate near the diagonal. Right picture: the assembled MCP stack with recommended orientation. Here, lugs with crimped wires crimped are used. Please follow the next figures/directions to achieve such a detector mounting

After having safely fixed the contact cable(s) on the ceramic ring(s):

In this and the following assembly drawings, no cables are shown.

1. Place the front ceramic ring (metallization on both sides), with the contact for MCP front side pointing upward, with inserted plastic screws from below on a flat table:

Figure 1.10: Assembly of MCP-stack - Stage 1 (DLD40, DLD80 & HEX80)

2. Remove one MCP (for first stage of the stack) carefully from its transport package and place it centered onto the ceramic ring. Unless otherwise noted any of the delivered MCPs can be used for this and will have a mark on the outer rim defining the input (front) side, indicating the MCP pores' tilt angle in the azimuthal plane. This side has to face down and will be in contact with the front ceramic ring. Remember the position of the mark. The second (and possibly a third) MCP will be placed with its mark also facing down and should be rotated by about 180 azimuthal degrees with respect to the mark position on the MCP under it. In a side view cross section of the stack, the pores of the MCP would resemble a (broad)

"v" shape (or chevron), or a "z" shape for triple stacking. Such an angle orientation is very important for proper stack performance, however, any relative azimuthal angle between 150° and 210° will serve as well as having exactly 180° between marks.

Figure 1.11: Assembly of MCP-stack - Stage 2a (DLD40, DLD80 & HEX80)

A shim ring may be placed between the MCP stages of the stack. Usually, the delivered MCPs will be matched in resistance within 10% for direct stacking. If not, a shim ring *with contact lug* must be used with cable connection to a feedthrough for bias via a high voltage supply. Please contact **RoentDek** in such a case. However, even for matched MCP placing a shim ring can be recommended.

- **DLD40**, **DLD80**, **HEX75** with 60:1/40:1 MCP: there is no intermediate contact ring recommended, the second (and possibly third) MCP can be placed in direct contact with each other.

- **HEX80** with 60:1 MCP: a shim ring can optionally be supplied to reduce the active MCP diameter to 75mm. This is beneficial for some multi-hit applications.

- **DLD40EP/DLD75eT**, **HEX75eT** with 80:1 MCP: a shim ring may be used for reducing ion feedback and increased gain at lower bias (but may affect temporal resolution adversely).

Figure 1.12: Assembly of MCP-stack - Stage 2b (DLD40(/2), DLD80 & HEX80/HEX75)

After possibly placing a shim ring on the first MCP the second (and optionally third) MCP can be stacked on top of the first one, observing the position of marks (see above). Dust particles that may have settled on MCP surfaces can usually be blown away by dry air over the surface.

# It is especially important to avoid that dust particles settle between the MCP during assembly.

Touch MCPs only with care along the rim, preferably with gloves. See also the Appendix of this manual for general MCP handling. After the stack is piled you have to check if it is well centered, adjustments can be done by carefully shifting individual MCPs sideways.

3. Place the second ceramic ring (with the MCP back contact facing down) carefully on the MCP-stack. The plastic rods will guide the alignment.

Note, that the contact positions on the two ceramic rings must not oppose each other.

Figure 1.13: Assembly of MCP-stack - Stage 3-1 (DLD40, DLD80 & HEX80)

Now fix the stack with the plastic nuts gently and very carefully. Use only so much force ("hand-tight") that the rings and MCP cannot move any more.

Figure 1.14: Assembly of MCP-stack - Stage 3-2 (DLD40, DLD80 & HEX80)

The MCP holder stack can now be finally fixed with 4 spring clamps. Make sure that one of the rings is close to the cable contact of the back ring and the other three at about 90° relative angle to that (see Figure 1.9). No clamp should be right at the position of a contact pad on any side of the rings.

Figure 1.15: Assembly of MCP-stack - Stage 3-3 (DLD40, DLD80 & HEX80)

Now remove the plastic screws again. The MCP holder stack can be used as an independent unit.

Figure 1.16: Assembly of MCP-stack - Stage 3-4 (DLD40, DLD80 & HEX80)

For MCP stacks with 3mm thickness the MCP back side can be contacted by a special spring clamp. Insert it between the rings at the position of a contact pad around a hole on the rear ceramic ring, i.e. electrically in contact with MCP back. Make sure that MCP front ring has no contact pad on the opposing side at the same position. The spring clamp has a 1mm stub for a connector (obtainable from **Excentiblek**).

Figure 1.17: MCP stack with spring clamp for the MCP back cable (DLD40, DLD80 & HEX80)

4. Now the MCP-stack can be mounted to the anode by inserting it into the butterfly-shaped indent of the holder plate and fixing it with the movable shields. Only uncoated parts of the ceramic ring shall rest on the holder plate, i.e. the spring clamps and protruding contacts from the back ring must be located along the diagonal of the plate, not touching it.

Figure 1.18: Assembly of MCP-stack - Stage 4 (DLD40 & DLD80)

Check with an Ohm meter that there is no electric contact between "MCP back", "MCP front" and "holder" plate. There should be a resistance in the  $10\text{-}100\text{M}\Omega$  regime between "MCP back" and "MCP front". In the presence of humidity the MCP stack resistance may be less than the default value.

For disassembly reverse all steps.

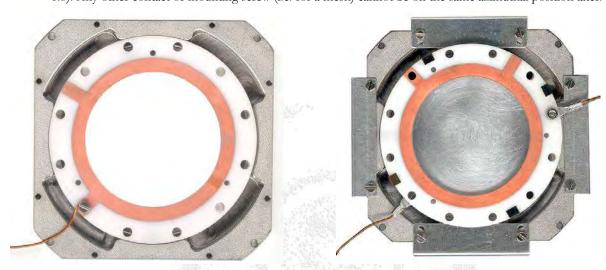

For the **HEX80**, the same butterfly-shaped MCP holder plate as for the **DLD80** is used. Additionally, a hexagonally-shaped intermediate plate connects the standard **DLD80** holder with the **Hexanode**. The shields are replaced by a pair of metal sheets that hold the MCP stack in position.

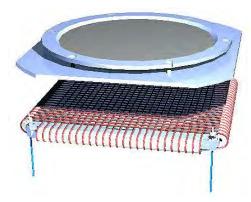

Figure 1.19: Hexanode with holder

Figure 1.20: Hexanode with mounted MCP-Stack

#### 1.2.4.2 Assembly of the MCP-stack for the DLD120 and HEX120

A cartoon about the mounting of the MCP stack for the **DLD120** and **HEX120(100)** can be found on our web-site in the MOVIES section. There you can also find cartoons showing the mounting of the MCP stack to the anode.

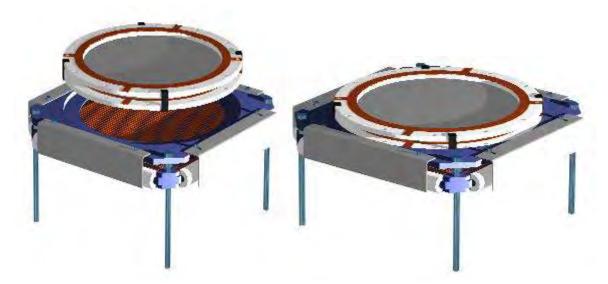

For the 120mm MCP size (or 100mm) the mounting is different than for the 40 or 80mm MCP sizes, no ceramic rings are used. Instead, the MCPs are fitted between a metal square-shaped rear plate which mates to the delay-anode and a metal front ring. The rear plate and the front ring have an indention for the MCP on one side. The MCP stack is fixed by 6 special M3 screws make from PEEK which is an insulating UHV-compatible polyimide material.

Only on older systems M2 rods from the same material are also used to fix the MCP stack to the anode.

For newer systems (without polyimide M2 rods) it is not necessary to remove the pre-mounted MCP rear plate from the anode for mounting of the MCP now:

1. Place the rear plate with the indention for the MCP pointing upward according to the sketch below. Screw the three M3 guide rods symmetrically into three of the six M3 tapped holes. Remove the MCP carefully from their transport package and insert the first one (the designated rear MCP in the stack) centered into the indention, with the bias angle marker (triangle on the outer rim on one side) pointing upward. For MCP general handling see also instructions in the Appendix of this manual. Touch MCPs only with care along the rim, preferably with gloves.

Unless otherwise noted, any of the supplied MCP can be selected for the position in the stack. The second (and possibly a third) MCP will be placed with its mark also pointing upwards and should be rotated by about 180 azimuthal degrees with respect to the mark position on the MCP under it. In a side view cross section of the stack, the pores of the MCP would resemble a (broad) "v" shape (or chevron), or a "z" shape for triple stacking. Such an angle orientation is very important for proper stack performance, however, any relative azimuthal angle between 150° and 210° will serve as well as having exactly 180° between marks.

Optionally, shim rings can be supplied for being placed between MCP which may improve overall gain homogeneity and (for **HEX120**) shall reduce the active MCP diameter to 100mm (which is beneficial for some multi-hit applications). Usually, the delivered MCPs will be matched in resistance within 10% for direct stacking. If not, a shim ring with contact lug must be used with cable connection to a feedthrough for bias via a high voltage supply. Please contact **RoentDek** in such a case

Figure 1.21: Rear metal plate with one MCP (DLD120 and HEX120)

After stacking the second (and possibly third) MCP carefully onto the first (with the bias angle marker pointing upwards and rotated with respect to the lower MCP's mark by about 180°) make sure that the MCPs are well-aligned with each other and are centered in the indention, adjustments can be done by carefully moving the individual MCPs on the ring.

## It is especially important to avoid that dust particles settle between the MCP during assembly.

Dust particles that may have settled can usually be blown away be spraying dry air across the MCP surface.

Figure 1.22: Assembly of MCP-stage 2 (DLD120 and HEX120)

If the MCPs need replacement mount a set with matching electrical resistance only or employ a shim ring with contact lug for intermediate bias (see above).

2. Place the front metal ring with the indented side facing downward on the MCP. The guide pins will help in the alignment. It is very important that the MCP stack is well centered and will fit into the indention of the front ring.

Figure 1.23: Assembly of MCP-stack - Stage 3-1 (DLD120 and HEX120)

Now fix the stack with three plastic screws very carefully and only lightly. Due to the indentions in the rear plate and the front ring, the MCP will not fall out even if the screws are not entirely tight. Remove the guide pins and add the other three screws. Once all screws are in place fix them again slightly without excessive force

Figure 1.24: Assembly of MCP-stack - Stage 3-2 (DLD120 and HEX120)

Figure 1.25: Assembly of MCP-stack - Stage 3-3 (DLD120 and HEX120)

3. Now the MCP back contact cable can be fixed to the rear metal plate on any of the M2 threads along the edges.

The MCP front contact cable can be fixed to the front ring likewise on a M2 threaded hole or as in Figure 1.25. For this remove the screw from the whole with the gap for the cable, insert the MCP front contact cable and re-fix the screw as tight as the others.

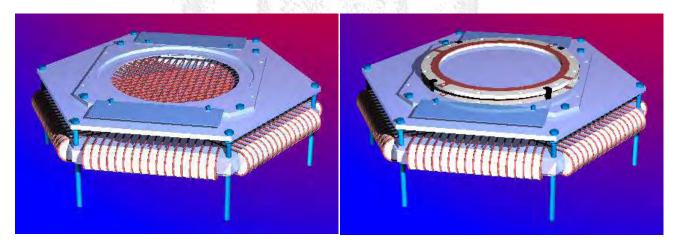

On older systems, the mounted MCP stack now has to be fixed to the anode via Vespel M2 rods in the corners of the delay-line anode using nuts on either side of the corresponding mounting holes in the rear plate (or the wing rails in case of **HEX120**). It is only necessary to sink the M2 polyimide rods by 3-4mm into the anode body, so that they are safely fixed.

Figure 1.26: Assembly of MCP-stack - Stage 4 (DLD120 and HEX120) only for old systems

The recommended distance between the MCP back plate and the anode body plate is about 8mm.

A woven potential mesh wMesh120 can be supplied for being placed on the MCP front side. Please contact **RoentDek** for this option.

# 2 Mounting of the Detector and cable connections via vacuum feedthrough

**RoentDek** provides the **FT12** and **FT16** products (with or without mounting option) to allow a proper cable feeding through the vacuum wall. The **FT16** is a combination of an **FT12** feedthrough and an **FT4** feedthrough (the latter also used for the **DET40/75** timing detectors). These products can be completed by airside decoupling circuits forming the **FT12TP** and **FT16TP** products (not for operation with older **DLATR6/8** units). The maximum voltage rating of the **FT12** and the standard **FT4** feedthroughs is 4kV, likewise, the flange mounting is also specified up to this rating\*. The detector can either be custommounted to an experimental setup or to a mounting flange. **BDentDek** provides a product option for each detector type for mounting it onto a flange of "Conflat" norm. The minimum (and default) size of the flange is given by the detector dimension. However, mounting on larger flanges are possible and often beneficial.

If you do not want to or cannot mount the detector in such a way it is strongly recommended to still use the **RoentDek FT12TP** or **FT16TP** cable feedthrough(s) and signal decoupling plugs. For a custom mount to an existing experimental setup we recommend using the outermost threaded holes (in the "holder") to fix the detector to your experimental setup, e.g. employing the supplied threaded rods in the shipping mount. Please note that the holder plate/the threaded rods will usually be biased during operation at a different potential than the mating part of your experimental setup. A proper insulation is needed. One (or two for **FT16TP**) DN35CF port(s) must be in the vicinity of the detectors (distance <50cm).

Notice: It is important to have at least 2mm distance between any part of the detector and any other metal part of a setup, unless the voltage difference is small during operation.

As a thumb-rule, at least 1mm distance for every 1000V of voltage difference should be allowed, assuming also absence of sharp edges or tips.

If this is not fulfilled, discharge can occur during operation with the consequence of possible damage of the detector or the electronics.

One can use sheets of Kapton for security if distances appear too small for safe operation. Please contact **RoentDek** for options.

The vacuum port where the detector is mounted must have at least 100mm open diameter for DLD40, 150mm for DLD80, 200mm for HEX80/HEX75 and DLD120 and 250mm for HEX120 and DLD150. If the detector shall come to rest within the port/tubing of this minimum diameter it may be required to care for extra insulation.

### 2.1 Mounting of the Detector on a Vacuum-Flange

If you have purchased the flange mounting option fix the stainless steel support ring via the outer threaded M2 rods to the delay-line anode. You may use one of these thread bolts to supply the anode holder voltage with an appropriate cable. Allow at least 30mm distance between support ring and delay-line anode.

Then mount the support ring with 8 ceramic insulators and 8 nuts using the M3 threaded bolts onto the flange. The threaded bolts are grinded at one end. This end must be on the flange side to avoid air pockets in the tapped holes of the flange. The **HEX80** and **DLD150**, **HEX120** or any other detector's mounting on a CF250 or CF300 flange, special M6-to-M3 adapter rods are provided.

Please note that the ceramic insulators will not tolerate excessive force when fixing the nuts.

Adjust everything parallel to the flange and fix the nuts. The height above flange of the detector can be varied by choosing specific distances for fixing the nuts on the M2 and M3 rods. Make sure to allow sufficient distance for slipping the wire contact pins for the delay-line-terminals on and off. In case you need to further reduce distance to the flange it is possible to alternatively contact the cable pairs by 2mm lugs and nuts on the wire terminal. Please see advice from **RoentDek** before choosing this option.

Additional cartoons and drawings about the mounting of the **DLD** and **HEX** detector to a mounting flange can be found on our Web Site.

<sup>\*</sup> Please contact **RoentDek** for options of biasing MCP front up to -6kV or for special mountings/signal decoupling rated to even higher voltage ("floated detector operation").

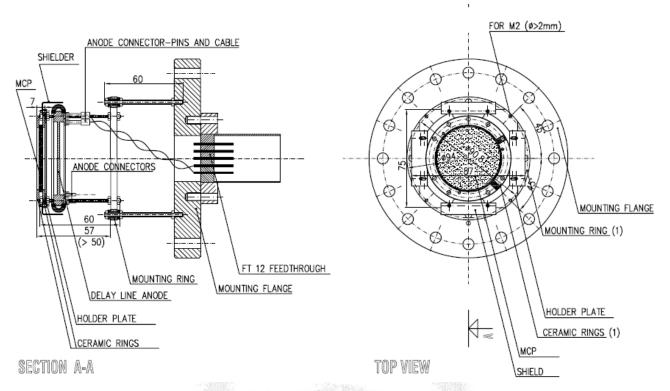

Figure 2.1: Sketch of the detector with mounting flange (only flange mounting option, here: FT12TP/100). For connecting a Hexanode, the same 12-pin feedthrough is used and an additional set of at least 3 MHV or SHV feedthroughs (e.g. the FT4) is needed for connecting the MCP front, MCP back, Holder (and optionally a mesh).

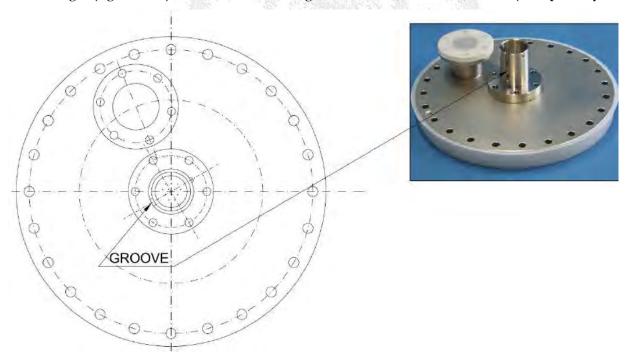

Figure 2.2: CF200 flange with two CF35 ports for mounting a Hex80 detector. It is recommended to fix the FT12 12-pin feedthrough on the center port in an orientation that the groove points perpendicular (or as close to that as possible) to the direction of the off-center port. This avoids spatial conflicts that can occur for certain item combination in the FT16TP product package.

# 2.2 Connecting the Signal Cables to a Feedtrough Flange

In the following the connection scheme to the **FT12** feedthrough flange is described. This flange is used for airside coupling to the **FT12TP(hex)** signal decoupling plugs. The following connection schemes are also compatible with earlier read-out concepts (**FT12/16** with **DLATR6/8**). For the **DLD** detectors the **FT12** offers also feedthrough leads for the remaining detector contacts (i.e. for the MCP and Holder), with **HEX** detectors require additional feedthroughs like in the **FT16** product assembly.

Unless you have purchased the flange mounted option you will usually receive a spool of Kapton isolated cables (for **DLD**) which can be used in UHV. You need to produce single and twisted-pair cables of sufficient lengths as described before in this section. The cables should only be as long as necessary. Especially the quality (amount of "ringing") of the MCP signal is usually better if the connection cable is very short. If you have purchased a Hexanode without flange mounting option you have receive a set of cables with two parallel wires (about 0.5m long) for connecting the Hexanode delay-line.

For the **DLD** connect all 8 cables from the delay-line and the other 3 (or 4) high voltage cables (MCP front, MCP back, anode holder plate and optional mesh) from the vacuum side of the feedthrough flange. Figure 2.3 shows the **FT12** flange from the vacuum side.

Figure 2.3: Pin numbers at the FT12 flange (the airside guiding groove points upwards) and cable connections.

Unless you have purchased the flange mounted option you will usually receive a spool of kapton-shielded cables which can be used in UHV. You may need to produce single and twisted-pair cables of sufficient lengths as described before. The cables should only be as long as necessary. Especially the MCP signal quality (amount of "ringing") is usually improved if the connection cables are kept as short as possible.

For the **DLD** connect all 8 cables from the delay-line and the other 3 (or 4) in vacuum cables for MCP front, MCP back, anode holder plate and optional mesh from the vacuum side of the 12-pin feedthrough flange according to Table 2.1. In case of a Hexanode detector, the 12-pin feedthrough is only used for the anode terminals (according to Table 2.2 while the other detector contacts are connected via separate feedthroughs, e.g. the **FT4** which is part of the **FT16(TP)** or via individual coaxial SHV or MHV feedthroughs.

| Pin number  | Function                  | FT12TP  | FAMP8/CFD8b    | ATR19          | HM1/TDC8HP  |

|-------------|---------------------------|---------|----------------|----------------|-------------|

| FT12 flange |                           | channel | channel        | channel        | channel     |

| No. 1       | X (e.g. Mesh)             |         |                |                |             |

| No. 2       | MCP front                 | No. 1   | No. 7 or No. 8 | No. 1 or No. 2 | "start" / 8 |

| No. 3       | MCP back                  | No. 2   | No. 7 or No. 8 | No. 1 or No. 2 | "start" / 8 |

| No. 4       | Anode Holder              |         |                |                |             |

| No. 5       | x <sub>1</sub> -reference | No. 3   | No. 3          | No. 3          | x1 / 1      |

| No. 6       | x <sub>2</sub> -signal    | (No. 4) | (No. 4)        | (No. 4)        |             |

| No. 7       | x <sub>2</sub> -reference | No. 4   | No. 4          | No. 4          | x2 / 2      |

| No. 8       | x <sub>1</sub> -signal    | (No. 3) | (No. 3)        | (No. 3)        |             |

| No. 9       | y <sub>1</sub> -reference | No. 5   | No. 5          | No. 5          | y1/3        |

| No. 10      | y <sub>1</sub> -signal    | (No. 5) | (No. 5)        | (No. 5)        | •           |

| No. 11      | y <sub>2</sub> -reference | No. 6   | No. 6          | No. 6          | y2 / 4      |

| No. 12      | y <sub>2</sub> -signal    | (No. 6) | (No. 6)        | (No. 6)        | •           |

Table 2.1: FT12TP pin description for DLD detectors

The red oval marks in Figure 2.3 define the pins for twisted cable pairs (1/4 and 3/2 pairs only for Hexanode). When connecting the delay-line anode please give special attention to the assignment of neighboring pins 5 and 76 which are NOT attributed to cable pairs from the same anode terminal, likewise for pins 1 and 2 in case of the Hexanode.

| Pin number  | Function                  | FT12TP hex | FAMP8/CFD8b | ATR19   | TDC8HP/fADC |

|-------------|---------------------------|------------|-------------|---------|-------------|

| FT12 flange |                           | channel    | channel     | channel | channel     |

| No. 1       | z <sub>1</sub> -reference | No. 1      | No. 1       | No. 7   | 5           |

| No. 2       | z <sub>2</sub> -signal    | (No. 2)    | (No. 2)     | (No. 8) |             |

| No. 3       | z <sub>2</sub> -reference | No. 2      | No. 2       | No. 8   | 6           |

| No. 4       | z <sub>1</sub> -signal    | (No. 1)    | (No. 1)     | (No. 7) |             |

| No. 5       | x <sub>1</sub> -reference | No. 3      | No. 3       | No. 3   | 1           |

| No. 6       | x <sub>2</sub> -signal    | (No. 4)    | (No. 4)     | (No. 4) |             |

| No. 7       | x <sub>2</sub> -reference | No. 4      | No. 4       | No. 4   | 2           |

| No. 8       | x <sub>1</sub> -signal    | (No. 3)    | (No. 3)     | (No. 3) |             |

| No. 9       | y <sub>1</sub> -reference | No. 5      | No. 5       | No. 5   | 3           |

| No. 10      | y <sub>1</sub> -signal    | (No. 5)    | (No. 5)     | (No. 5) |             |

| No. 11      | y <sub>2</sub> -reference | No. 6      | No. 6       | No. 6   | 4           |

| No. 12      | y <sub>2</sub> -signal    | (No. 6)    | (No. 6)     | (No. 6) |             |

Table 2.2: FT12(TP) pin description for HEX detectors

Verify proper anode cabling with an Ohm meter. Check for

- proper resistance between the ends of all wires (e.g. between pin 5 and pin 7),

- absence of shorts of any wire to ground or to any other detector part,

- absence of shorts between any of the wires,

- absence of shorts between the other detector parts.

A "short" in this respect is any resistance  $\leq 10 M\Omega$  (except for the resistance between MCP back and front, which may be smaller, see next section).

If you perform these checks from the air side of the feedthrough make sure to identify the pin numbers correctly (mirror-inverted compared to Figure 2.3). **RoentDek** can supply a test plug to ease this verification task. Some of the tests can be done more efficiently via the **RoentDek** signal decoupler plug (see next section). A cabling error which cannot be detected by verifying the cables with an Ohm meter from the feedthrough air-side alone (e.g. when the parts in vacuum are not accessible any more) is for example a swap between pin 6 and 8.

If a connector pin is too close to the chamber wall or a neighboring pin, this may result in a discharge during detector operation, with consequences to the electronics and detector (see above). In case of **DLD** please give extra attention to pins 1 and 2, which can have especially high potential relative to the others.

# 2.3 The FT12TP (hex) - Feedthrough Flange with Signal Decoupler

The FT12TP feedthrough and signal decoupling option allows using any adequate amplifier and timing discriminator or recording electronics to operate a **RoentDek DLD** (or HEX, see also FT16TP in the next section). Examples for adequate amplifier/CFD are the **RoentDek ATR19** units or the FAMP1/3/6/8 (amplifier only, with output to CFD or fast-ADC follow-up electronics).

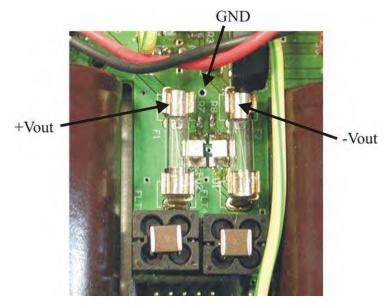

The **FT12TP** for DLD contains the standard 12 pin feedthrough **FT12** for the in-vacuum cables as described above and an air-side connector plug. The plug provides adequate RC decoupling circuits and special transformer circuits to turn the differential delay-line signals into single-line signals with  $50\Omega$  line impedance output connectors. The detector voltages are supplied via SHB input cables sockets:

U<sub>Reference</sub> Reference wires' bias U<sub>Signal</sub> Signal wires' bias

U<sub>Holder</sub> Anode-plate (Holder) bias, not in hex-version

U<sub>MCP front</sub> MCP front bias, not in hex-version U<sub>MCP back</sub> MCP back bias, not in hex-version

U<sub>X</sub> optional "X" potential, can be used for a mesh or intermediate MCP bias, not in hex-version

The "raw" (unamplified) signals from the MCP contact and/or delay-line contacts are delivered to five LEMO 00 series type connectors\*.

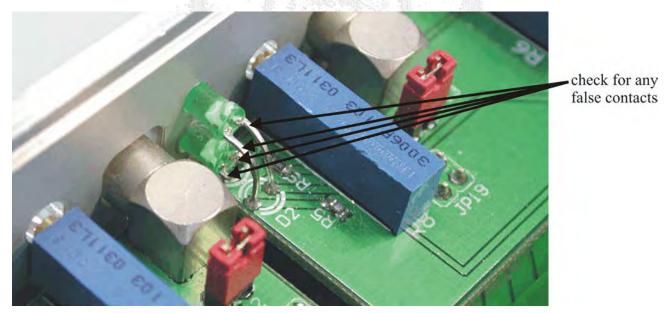

Adjustable resistors (potis  $0-200\Omega$ ) for "Holder" and "X" contact and for the MCP allow improving signal quality from an MCP contact. The standard FT12TP decoupling plug has a switch for selecting the source of the MCP signal, i.e. optional pick-up from MCP front contact or MCP back contact. The other side of the MCP is then connected to the terminating poti. An in-line resistor can be adjusted from the side and changes the pulse height of the MCP signal but also alters the signal shape in combination with the other potis. Fine-tuning these potis will result in a decent MCP signal shape adequate for further electronic processing in follow-up timing electronics. Note that the signal outputs from MCP front and back can have different shapes and require different fine-tuning. Any metal part (biased mesh, electrode) close to the MCP can affect the signal shape and it is recommended to place a signal termination circuit on it, too. The "X"-line of the **FT12TP** poti.

Figure 2.4: FT12TP Plug with switch for front (f) and back (b) MCP pickup. The hole in the ring case allows access to the in-line poti.

The so-called FT12TPhex plug for the Hexanode is very similar to the FT12TP for DLD but has 6 lemo outputs for the delay-line anode signals and two SHV bias inputs for U<sub>ref</sub> and U<sub>sig</sub>. It serves as connector/decoupling unit only for the Hexanode while the bias and signal pickup to the remaining parts of the detector is routed via different feedthroughs and decoupling/terminating circuits. The FT12TPhex circuit can also be supplied in a square-shaped case which contains more flexible circuits, i.e. one can use an alternate biasing scheme for special detector setups and it allows a differential signal transmission to special amplifiers via CAT7 cables, see Figure 2.5.

Figure 2.5: FT12TPhex plug with square case

When the FT12TP(hex) plug is connected to the delay-line it is possible verifying the absence of shorts between signal and reference wires or some of the possible cabling errors on the vacuum side of the feedthrough: The resistance between  $U_{ref}$  and

<sup>\*</sup> In case you have an older **FT12TP** plug for use with **DLD** with 6 lemo sockets (and 6 SHV connectors) please refer to the manual that came with this delivery or ask **RoentDek** for a manual of old-type **FT12TP** assemblies.

$U_{sig}$  SHV inputs should exceed 10M $\Omega$ . A resistance value on the order of 1-2M $\Omega$  or less indicates a cabling error or a short on the delay line. Please note that some other possible misconnections on the feedthrough may not be found by this test.

Likewise, the presence of shorts between other parts of the detector or from parts to ground will be revealed by a <10M $\Omega$  "short" if measured through the SHV inputs of the decoupler circuits (assuming that all connections are in place). Exception: between properly connected MCP front and MCP back input one can measure a resistance on the order of the expected MCP stack resistance which may be <10M $\Omega$  in some cases, especially when the detector is still exposed to ambient air. In case of the **FT12TPhex** please also refer to the next section for this test.

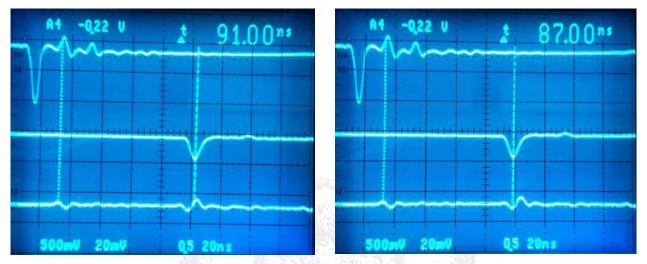

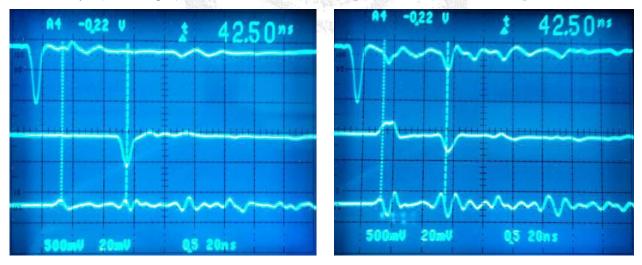

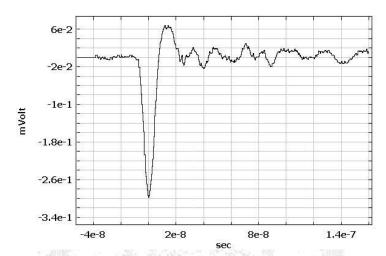

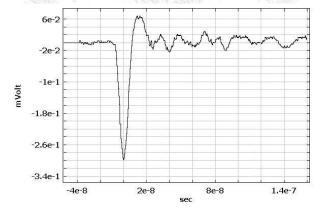

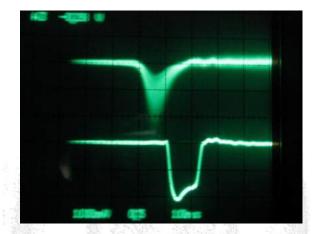

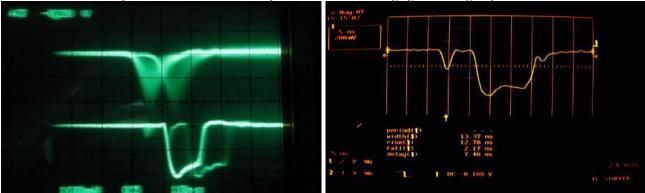

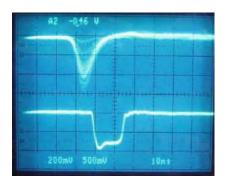

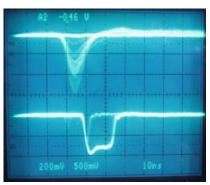

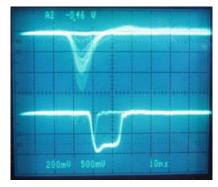

With the help of a fast signal pulse generator (e.g. the **RoentDek** APG1) one can send a signal via an (output) lemo connector (e.g. x1) of the **FT12TP(hex)** through a delay-line layer and verify the (delayed and slightly damped/distorted) response signal from the (x2) output with an oscilloscope (see figure 2.6, the same check can be done for the other layers). Most wiring errors will be revealed by a strongly distorted signal response.

Figure 2.6: Response of a delay-line to a signal passing through a FT12TP(hex) plug. Upper trace: input signal, middle trace: output signal from the opposing terminal of the same layer, lower trace: output from a terminal of another layer (25x enlarged). The left marker defines the input time reference. Further explanations see text.

Figure 2.6 shows in the upper two images signals transmitted through the **DLD80** anode layers via the **FT12TP** connector (left picture: outer layer, i.e. via  $x_1/x_2$ , and inner layer on right picture). A correctly connected anode will show a slightly damped output signal response (middle trace), delayed according to the delay-line transmission time (plus offset from connection cables). The cross talk to another layer (lower trace) is small. The lower left image shows the same for a **DLD40**. If the connections between pin 6 and 8 are swapped as in the right lower picture the response is clearly different.

#### Blocking resistors:

An integral part of most signal decoupling circuits is a serial resistor in the connection line between the MCP stack and the bias input, e.g. from the high voltage supply. The resistor forms a chain with the MCP stack resistance (and more resistors in the line, e.g. a serial resistor on the other MCP stack side) and alters the effective potential present on the MCP surface: it is shifted by a value  $\Delta U$  towards the potential on the other MCP side, compared to the set potential coming from the high voltage supply. These serial resistors are usually small compared to the MCP resistance but the effect cannot always be neglected.

$$dU_{MCP\ front} = \Delta U_{MCP} \times \frac{R_{Df}}{R_{MCP} + (R_{Db} + R_{Df})}$$

Equation 2.1

$$dU_{MCP\ back} = \Delta U_{MCP} \times \frac{R_{Db}}{R_{MCP} + (R_{Db} + R_{Df})}$$

$dU_{MCP}$  front/back are the potential shifts between set and effective potential on the MCP stack ends,  $R_{MCP}$  is the MCP stack resistance and  $R_{Df}/R_{Db}$  the serial resistors' values in the respective decoupling circuits and  $\Delta U_{MCP}$  is the set voltage difference across the MCP ( $\Delta U_{MCP} = U_{MCP\ back} - U_{MCP\ front}$ ). Usually, the term ( $R_{Df} + R_{Db}$ ) can be neglected in the denominator of the equations.

Example:

$$R_{MCP} = 60 \text{ M}\Omega, R_{Df} = 10 \text{k}\Omega, R_{Db} = 1 \text{M}\Omega, U_{MCP \text{ front}} = -600 \text{V}, U_{MCP \text{ back}} = +1800 \text{V}$$

$$\rightarrow U_{MCP \text{ front effective}} = -599.6 \text{V}, U_{MCP \text{ back effective}} = +1760 \text{V}, \Delta U_{MCP \text{ effective}} = 2360 \text{V}$$

In the **FT12TP** decoupler  $R_{Df}$  and  $R_{Db}$  are  $10k\Omega$  and  $1M\Omega$ , respectively, older **FT12TP** plugs may have  $1M\Omega$  as default value for both sides, also like the standard **BoentDek FT4TP** with **HFSD** and **HFST** single line decouplers (see next section). It is possible to measure the actual resistance values with an Ohm meter between the high voltage input socket and the pin that connects to the respective feedthrough. The sum  $(R_{MCP} + R_{Df} + R_{Db})$  can also be measured through the decoupler's high voltage inputs for  $U_{back}$  and  $U_{front}$  if all connections to the MCP are made. Note that the measured value  $R_{MCP}$  can differ compared to operation conditions if the stack is at atmospheric pressure.  $R_{MCP}$  is also temperature dependent.

Attention: Although the outputs of the FT4TP and FT12TP are delivered with DC-coupling to ground potential, a discharge on a detector can damage the electronics which is used to analyze or amplify the signals.

Before vacuum-baking of the experimental setup all air-side connections on the FT12 and FT4 feedthroughs must be removed. The FT12TP plugs and HFSD/T connectors are not rated for typical bake-out temperatures

# 2.4 The FT4(TP) for FT16(TP) and DET40/75

For the **RoentDek** HEX detector and the timing detectors of type **DET40/75** the **FT4**, a four-fold MHV feedthrough set (optionally SHV) on CF35 flange is used to supply cable contacts to MCP front, MCP back, Holder (or the timing anode, respectively) and an optional mesh. For signal pickup or termination, individual *HF-signal-de-coupler plugs* (HFSD/HFST) (Figure 2.7) for each detector contact can be provided to complete the product set **FT4TP**. This combines with the **FT12TPhex** to the **FT16TP**. The *HF-signal-de-coupler plug* for the Hexanode "Holder" is of type HFST and has a signal terminating poti. The same type is used on one of the MCP contacts, while the other MCP contact (and the timing anode contact, respectively) is supplied via a HFSD signal decoupler with a lemo output socket for the signal to further process it to an amplifier and timing circuit. An *Adjustable LEMO Terminator* (AST) can be optionally supplied to turn a **HFSD** into a double-use unit (as **HFSD** or **HFST**). The latest version of the **HFSD** has a poti in the signal line (see red arrow in Figure 2.7) which can also be used to improve the signal quality in combination with the other potis (like with the **FT12TP** connector plug and **DLD**)\*. Optionally, the **HFSD** and **HFST** can be supplied with a  $10k\Omega$  serial resistor in the line to the high voltage power supply (default is  $1M\Omega$ ).

<sup>\*</sup> On older systems the **HFSD** needs to be opened for accessing the in-line poti. Although most care has been taken to insulate all high voltage holding parts of the circuit for your safety please be careful to *only touch the poti screw* and *only with an insulating screw driver* when operating on an open **HFSD**.

Figure 2.7: Single HF-signal-de-coupler plug (HFSD) with LEMO output and in-line poti

The *HF-signal-de-coupler plugs* can also contain an additional resistor to ground which provides the **HVT** function (see **IROENTDEK** power supply manual which may be appended to this document).

# 2.5 Operation of the MCP detector with delay-line (or timing) anode

This introduction to the MCP detector operation shall only give general info on the detector startup and basic function verification. For fine-tuning please refer to the specific sections describing the front end electronics (amplifier and timing circuits), digital read-out and high voltage supply, e.g. as optionally available from **RoentDek**.

If you have purchased a detector for operation at higher voltages than 4kV please refer to the separate manual.

### 2.5.1 Initial Startup Procedure

After installation of the detector and verification of all connections it is advisable to verify the absence of electronic noise on the detector parts, i.e. on the MCP front/back and anode contacts. Continuous noise should be <1mV peak-to-peak. Noise should be checked by connecting an amplifier (band width about 100MHz or higher) to the outputs of the signal decouplers (high voltage supplies turned off) and verifying the amplified output on an oscilloscope (taking into account the amplification factor to judge the noise amplitude). If you should find a too-high noise level (or no noise at all) this may indicate erroneous cable connections. External sources for noise may be found in the lab equipment and can be traced by turning off lab equipment sequentially, or outside the lab/building (power stations, heavy machinery operating, radio stations ...).

This test can already be done before starting the vacuum pumps which may also contribute to the noise level.

For supplying the MCP operation voltages it is strongly recommended to use low-ripple power supplies with current limitation and fast shutdown for protection (as available from **RoentDek**).

Always evacuate the vacuum chamber slowly (50mbar/sec) in the presence of an MCP detector. The maximum recommended operating pressure for the detector is 2x10<sup>-6</sup>mbar).

Before applying any voltage to the detector for the first time it should be verified that:

- the detector is in appropriate vacuum conditions (< 10-6Torr) for at least 24h, see also Appendix

- all connections inside the vacuum are complete and have been carefully verified, also for absence of shorts

- safe distances are kept or sound insulation is installed between all biased parts of the detector (including attached cables) and the chamber wall and or other metal parts on ground or other potentials (i.e. mounting gear)

- safe distances are kept between the MCP front (and optional mesh) contacts and exposed cable parts to any other part of the detector (double-check also exposed cable/connector parts on the vacuum feedthrough)

- all feedthroughs, decoupling circuits and high voltage cables are rated for the targeted maximum detector voltage,

- potential EM noise sources are turned off

- UV sources, high power laser sources, charged particle sources (also ion gauges or ion pumps, discharge gaps) in the detector's vacuum recipient are turned off

New MCP or MCP that have been exposed to atmospheric pressure for a long time must be biased very slowly in steps of 100V every few minutes. During this, the current should be monitored for possible deviations from linear current-to-voltage characteristics (indicating a problem). As the operation voltage is approached, the amount of "dark counts" (MCP signals in absence of any particle/photon source) should be monitored. This requires a low noise level (see above). To monitor the noise and the presence of signals, an amplifier should be used for verifying signals from the MCP front or MCP back contact with an oscilloscope. A low dark count rate (typically <100counts/sec, randomly distributed) will at some point already indicate that the MCP is operating normally, especially when the mean pulse height increases/decreases according to the MCP bias setting.

A spontaneous discharge or a significantly higher dark count rate indicates a problem such as a glow discharge or the presence of charged particles/photons triggering the MCP. If this rate is excessive the MCP can be damaged. In such an event turn off the high voltage and verify your setup again. Note that it may occur that an excessive load of particles on the MCP detector is not detected by verifying the MCP signal because the MCP stack reaches current saturation before producing individual pulses of detectable signal height (i.e. above noise level). Such MCP saturation can usually be recognized from non-linear bias/current characteristics. Therefore we recommend using high voltage supplies with current reading, as available from **RoentDek**. Note, that some high voltage supplies may also increase the noise level, especially at high bias.

It is recommended to initially operate the detector in the so-called "ion mode" as used for detecting slow (and light) positive ions or fast (neutral) particles and photons, having MCP back at zero voltage to ground and the anode bias on few hundred Volts positive potential. At such potential discharge events on the "rear part" of the detector are virtually excluded. Only the MCP front side is at high negative potential and the risk for discharge (malfunction) from preparation mistakes is lowest. Remaining hazards are too-close metal parts in front of the MCP front face or at the cable contacts: nearby cable contacts should either be at least 3mm away or biased with the same potential for avoiding "sparks" (spontaneous discharges) and glow discharges which can occur from pointy parts already at relative potential well below the critical limit for spontaneous discharge.

| Typical | voltage | settings | 210 |

|---------|---------|----------|-----|

|         |         |          |     |

|                                             | Ion or Photon Detection | Electron Detection |

|---------------------------------------------|-------------------------|--------------------|

| MCP front                                   | -2400V                  | +300V              |

| MCP back                                    | 0V                      | +2700V             |

| Delay-line anode holder                     | 0V to 250V              | +2700V to +2950V   |

| Reference wires (respectively timing anode) | +250V                   | +2950V             |

| Collecting (Signal) wires                   | +300V                   | +3000V             |

Table 2.3: Typical detector voltage settings (chevron sets of 60:1 MCP). The (delay-line anode) "holder" potential needs to be carefully adjusted later to achieve optimal linear imaging performance at outer detection diameters